# **JVC** SERVICE MANUAL

# **DVD VIDEO PLAYER**

|                      | XV-M                                                | - <u>-</u> |                       |                                                     |

|----------------------|-----------------------------------------------------|------------|-----------------------|-----------------------------------------------------|

|                      | XV-M                                                | 50BK       | <b>`</b>              | [XV-M52SL]                                          |

|                      |                                                     |            |                       | Area Suffix                                         |

|                      | eer 3.<br>eer 2.<br>eer 1.<br>www.so. ord.co.p.aven |            |                       | B U.I<br>EN Northern Europ<br>UN Asea<br>US Singapo |

|                      |                                                     |            |                       | UW Brazil,Mexico,Pe                                 |

|                      |                                                     |            |                       | [XV-M50BK]                                          |

| Video CD             | TAL 3D-PHONIC                                       |            | OISC<br>DIGITAL AUDIO | Area Suffix                                         |

| <b>AV COMPU LINK</b> |                                                     |            |                       | UJ U.S.military                                     |

|                      | Each differe                                        | nce point  |                       |                                                     |

|                      | Model                                               | Body color |                       |                                                     |

Black

Silver

In regard with component parts appearing on the silk-screen printed side (parts side) of the PWB diagrams, the parts that are printed over with black such as the resistor (-----), diode (+---) and ICP (-) or identified by the " $\Delta$ " mark nearby are critical for safety. When replacing them, be sure to use the parts of the same type and rating as specified by the manufacturer. (Except the JC version)

XV-M50BK

XV-M52SL

#### Contents

| Safety precautions 1-2            | Disassembly n  |

|-----------------------------------|----------------|

| Preventing static electricity 1-3 | Adjustment me  |

| Precautions for Service 1-4       | Description of |

| Disassembly method       | 1-5  |

|--------------------------|------|

| Adjustment method        | 1-20 |

| Description of major ICs | 1-24 |

## -Safety Precautions

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (A) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

- 5. Leakage currnet check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.).

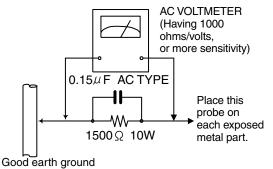

#### Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a 1,500  $\Omega$  10W resistor paralleled by a 0.15 $\mu$ F AC-type capacitor

between an exposed metal part and a known good earth ground. Measure the AC voltage across the resistor with the AC voltmeter.

Move the resistor connection to eachexposed metal part, particularly any exposed metal part having a return path to the chassis, and meausre the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. Voltage measured any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

### Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

In regard with component parts appearing on the silk-screen printed side (parts side) of the PWB diagrams, the parts that are printed over with black such as the resistor (--), diode (+-) and ICP (-) or identified by the " $\underline{\wedge}$ " mark nearby are critical for safety.

When replacing them, be sure to use the parts of the same type and rating as specified by the manufacturer. (Except the J and C version)

## **Preventing static electricity**

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

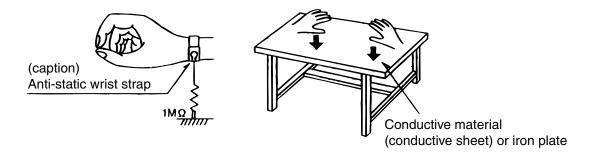

#### 1.1. Grounding to prevent damage by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as DVD players. Be careful to use proper grounding in the area where repairs are being performed.

#### 1.1.1. Ground the workbench

1. Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

#### 1.1.2. Ground yourself

1. Use an anti-static wrist strap to release any static electricity built up in your body.

#### 1.1.3. Handling the optical pickup

- 1. In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the next page.)

- 2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

#### 1.2. Handling the traverse unit (optical pickup)

- 1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

- 2. For specific details, refer to the replacement procedure in the text. Be careful not to take too long a time when attaching it to the connector.

- 3. Handle the flexible cable carefully as it may break when subjected to strong force.

- 4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it

## **Precautions for Service**

Handling of Traverse Unit and Laser Pickup

- 1. Do not touch any peripheral element of the pickup or the actuator.

- 2. The traverse unit and the pickup are precision devices and therefore must not be subjected to strong shock.

- 3. Do not use a tester to examine the laser diode. (The diode can easily be destroyed by the internal power supply of the tester.)

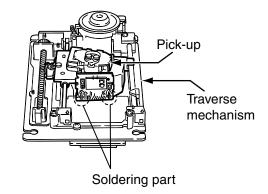

- 4. When replacing the pickup, after mounting a new pickup, remove the solder on the short land which is provided at the center of the flexible wire to open the circuit.

- 5. Half-fixed resistors for laser power adjustment are adjusted in pairs at shipment to match the characteristics of the optical block.

Do not change the setting of these half-fixed resistors for laser power adjustment.

Destruction of Traverse Unit and Laser Pickup by Static Electricity

Laser diodes are easily destroyed by static electricity charged on clothing or the human body. Before repairing peripheral elements of the traverse unit or pickup, be sure to take the following electrostatic protection:

- 1. Wear an antistatic wrist wrap.

- 2. With a conductive sheet or a steel plate on the workbench on which the traverse unit or the pick up is to be repaired, ground the sheet or the plate.

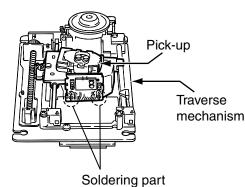

#### When you remove the traverse mechanism from the servo control substrate

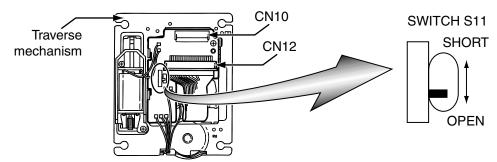

The laser diode of pick-up might be destroyed by static electricity and set switch (S11) on the pick-up board on "SHORT" side, please before removing the card wire from connector (CN10). Moreover, please set switch (S11) on "OPEN" side after assembling and inserting the card wire in connector (CN10) without fail at times.

#### When you remove the pick-up from the traverse mechanism

The laser diode of the pick-up might be destroyed by static electricity, and solder with part a, please before extracting a flexible wire from connector (CN12).

Moreover, please remove solder in part a after inserting a flexible wire in connector (CN12).

## **Disassembly method** <Main body>

the top cover.

power supply board.

the system control board.

assembly toward the front.

panel assembly on the bottom of the body.

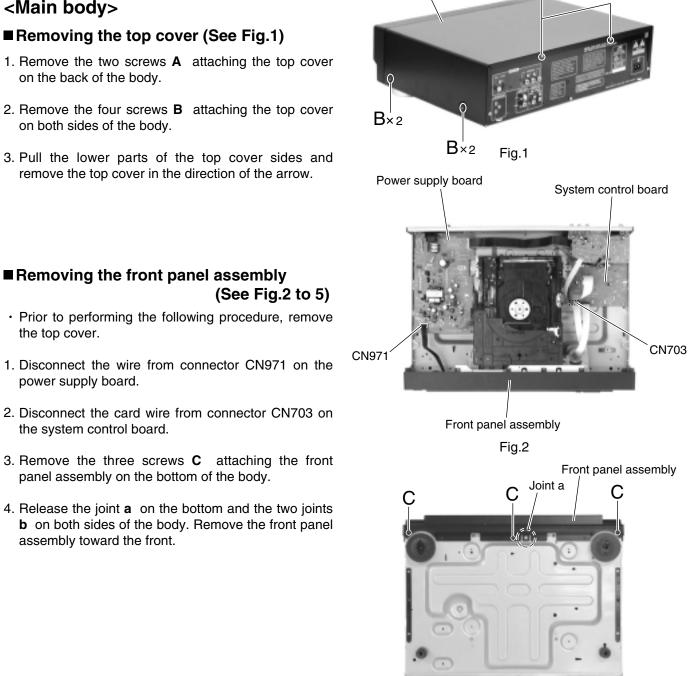

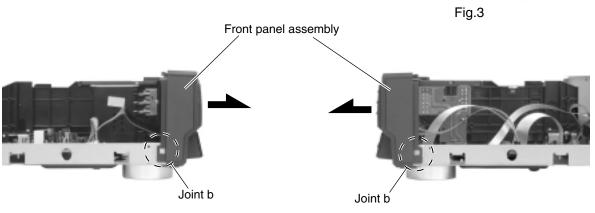

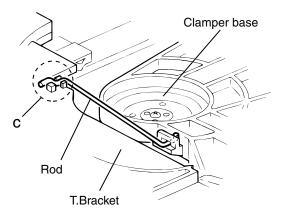

#### Removing the top cover (See Fig.1)

- 1. Remove the two screws **A** attaching the top cover on the back of the body.

- 2. Remove the four screws **B** attaching the top cover on both sides of the body.

- 3. Pull the lower parts of the top cover sides and remove the top cover in the direction of the arrow.

Top cover

Fig.5

#### XV-M52SL/XV-M50BK

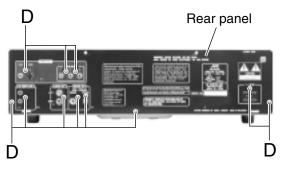

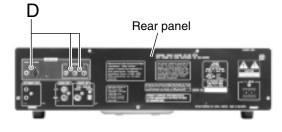

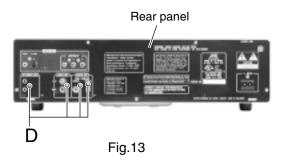

#### ■ Removing the rear panel (See Fig.6)

- Prior to performing the following procedure, remove the top cover.

- 1. Remove the eleven screws **D** attaching the rear panel on the back of the body and detach the rear panel.

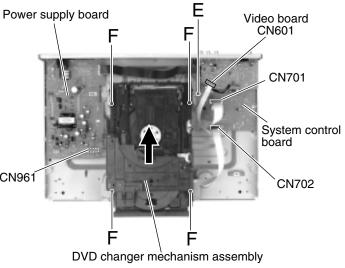

#### Removing the DVD changer mechanism assembly (See Fig.7)

- Prior to performing the following procedure, remove the top cover and front panel assembly.

- 1. Remove the one screw **E**.

- 2. Disconnect the 9 pin wire from connector CN961 on the power supply board.

- 3. Disconnect the card wire from connector CN601 on CN961 the video board.

- 4. Disconnect the card wires from connector CN701 and CN702 on the system control board.

- 5. Remove the four screws **F** attaching the DVD changer mechanism assembly.

- It is easy for removing the front panel assembly to remove the mechanism assembly though the mechanism assembly can be removed even in the state that the front panel assembly adheres.

Fig.7

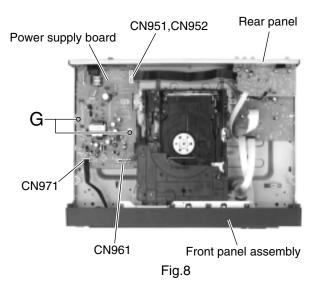

# Removing the power supply board (See Fig.8 and 9)

- Prior to performing the following procedure, remove the top cover.

- 1. Disconnect the wire from connector CN971 on the power supply board (The wire is extending from the front panel assembly).

- 2. Disconnect the 9 pin wire from connector CN961 on the power supply board (The wire is extending from the DVD changer mechanism assembly).

- 3. Disconnect the wire from connector CN951 and CN952 on the power supply board (The wire is extending from the system control board).

- 4. Remove the screw **D** attaching the AC jack on the rear panel.

- 5. Remove the two screws **G** attaching the power supply board and detach the power supply board.

Fig.9

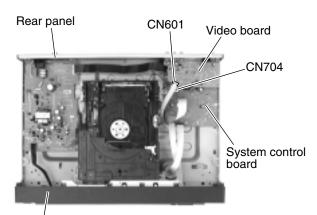

#### Removing the video board (See Fig.10 and 11)

- Prior to performing the following procedure, remove the top cover.

- 1. Disconnect the card wire from connector CN601 on the video board (The card wire is extending from the DVD changer mechanism assembly).

- 2. Disconnect the wire from connector CN704 on the system control board (The wire is extending from the video board).

- 3. Remove the three screws **D** attaching the video board on the rear panel. Pull out the video board from the rear panel.

Front panel assembly

Fig.10

Fig.11

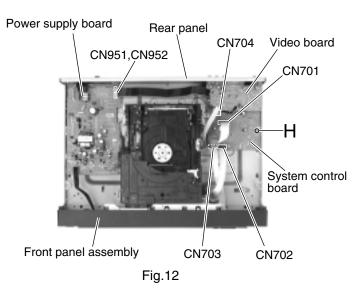

#### Removing the system control board (See Fig.12 and 13)

- Prior to performing the following procedure, remove the top cover.

- The system control board can be removed even if the video board is attached.

- 1. Disconnect the card wire from connector CN703 on the system control board (The card wire is extending from the front panel assembly).

- 2. Disconnect the card wire from connector CN701 and CN702 on the audio board (The card wires are extending from the DVD changer mechanism assembly).

- 3. Disconnect the wire from connector CN704 on the system control board (The wire is extending from the video board).

- 4. Disconnect the wire from connector CN951 and CN952 on the power supply board (The wire is extending from the system control board).

- 5. Remove the screw  ${\bf H}\,$  attaching the system control board.

- 6. Remove the four screws **D** attaching the system control board on the rear panel. Pull out the system control board toward the front.

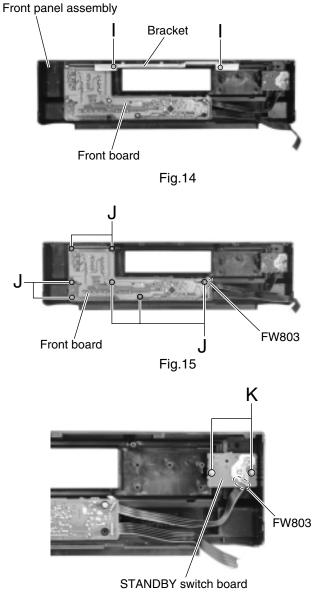

### <Front panel assembly>

• Prior to performing the following procedure, remove the top cover and the front panel assembly.

#### Removing the front board

#### (See Fig.14 and 15)

- 1. Remove the two screws I on the back of the front panel assembly and remove the bracket from the front panel assembly.

- 2. Remove the seven screws  ${\bf J}$  attaching the front board.

If necessary, unsolder FW803 and disconnect the wire.

# Removing the STANDBY switch board (See Fig.16)

1. Remove the two screws  ${\bf K}\,$  on the back of the front panel assembly.

If necessary, unsolder FW803 and disconnect the wire.

Fig.16

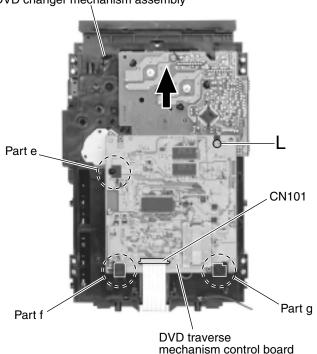

#### <DVD changer mechanism assembly> DVD changer mechanism assembly

- Prior to performing the following procedure, remove the top cover and the DVD changer mechanism assembly.

- Removing the traverse mechanism control board (See Fig.17)

- 1. Disconnect the card wire from connector CN101 on the traverse mechanism control board on the bottom of the DVD changer mechanism assembly.

- 2. Remove the screw L attaching the traverse mechanism control board. Release the three parts e, f and g and remove the traverse mechanism control board.

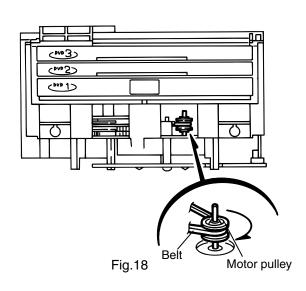

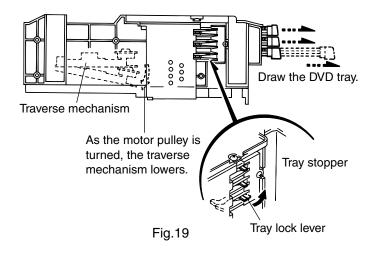

#### Ejecting the DVD (See Fig.18 and 19)

# ■When the DVD is set or the traverse mechanism is up.

% The DVD tray can not be ejected when the traverse mechanism is up.

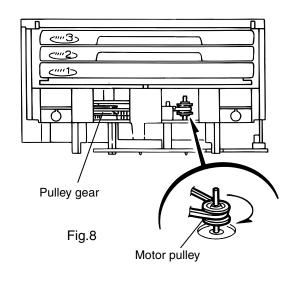

#### Bringing down the traverse mechanism as shown in the Fig.20

- 1. The motor pulley and the belt can be seen on the front side of the changer. Turn the motor pulley clockwise until the belt stops.

- 2. Pull the tray lock lever on the left side of the changer and draw the DVD tray.

- 3. Draw the DVD tray 1 to 3 as above.

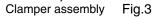

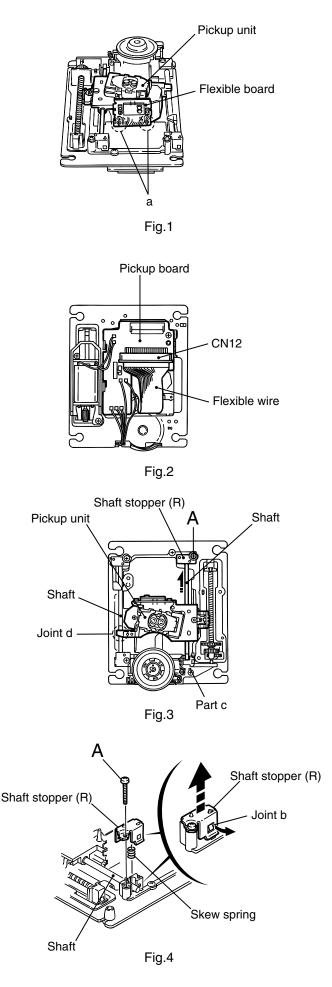

# <DVD Changer Mechanism Section> ■Removing the DVD mechanism board (See Fig.1)

- 1. Remove the DVD changer mechanism assembly.

- From bottom side the DVD changer mechanism assembly, remove the one screw A retaining the DVD servo control board.

- 3. Disconnect the card wire from the connector CN101 on the DVD servo control board.

- 4. Disengage the one engagement **a** and two engagements **b** , remove the DVD servo control board.

#### **ATTENTION !**

The laser diode of pick-up might be destroyed by static electricity and set switch (S11) on the pick-up board on "SHORT" side, please before removing the card wire from connector (CN101).

Moreover, please set switch (S11) on "OPEN" side after assembling and inserting the card wire in connector (CN101) without fail at times.

Please refer to page 1-4 for a detailed content.

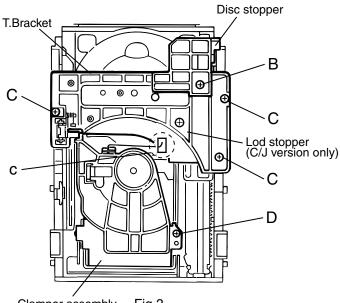

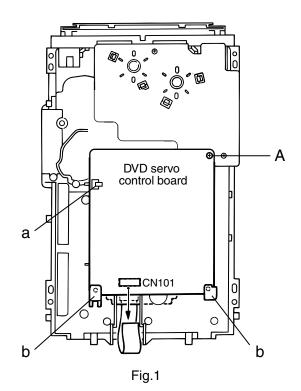

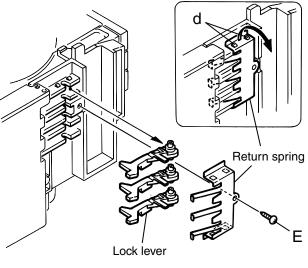

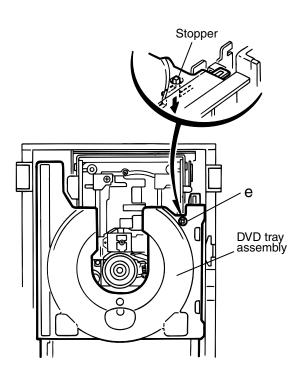

#### ■ Removing the DVD tray assembly (See Fig.2~4)

- 1. Remove the screw **B** retaining the Disc stopper (See Fig.3).

- 2. Remove the three screws **C** retaining the T.bracket (See Fig.3).

- 3. From the clamper base section **c**, remove both of the edges fixing the rod(See Fig.2 and 3).

- 4. Remove the screw **D** retaining the clamper assembly (See Fig.3).

- 5. From the left side face of the chassis assembly, remove the one screw **E** retaining both of the return spring and lock lever(See Fig. 4).

- 6. By removing the pawl at the section **d** fixing the return spring, dismount the return spring(See Fig.4).

- 7. Remove the three lock levers(See Fig.4).

Fig.4

#### XV-M52SL/XV-M50BK

- 8. Check whether the lifter unit stopper has been caught into the hole at the section e of DVD tray assembly as shown in Fig.5.

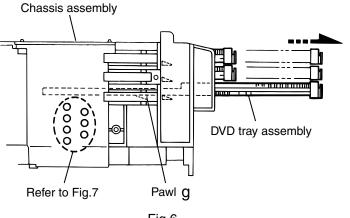

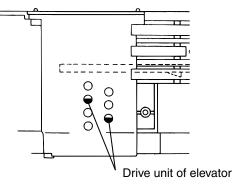

- 9. Make sure that the driver unit elevator is positioned as shown in Fig.6 from to the second or fifth hole on the left side face of the DVD Traverse mechanism assembly.

- [Caution] In case the driver unit elevator is not at above position, set the elevator to the position as shown in Fig.7 by manually turning the pulley gear as shown in Fig.8.

- 10. Manually turn the motor pulley in the clockwise direction until the lifter unit stopper is lowered from the section e of DVD tray assembly(See Fig.8).

- 11. Pull out all of the three stages of DVD tray assembly in the arrow direction **f** until these stages stop

(See Fig.6).

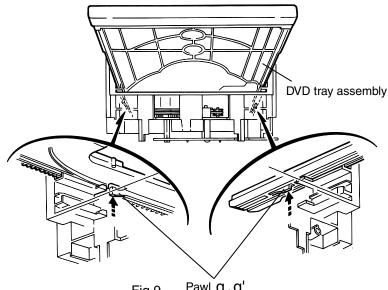

12. At the position where the DVD tray assembly has stopped, pull out the DVD tray assembly while pressing the two pawls g and g' on the back side of DVD tray assembly (See Fig.9). In this case, it is easy to pull out the assembly when it is pulled out first from the stage DVD tray assembly.

Fig.7

Pawl g, g Fig.9

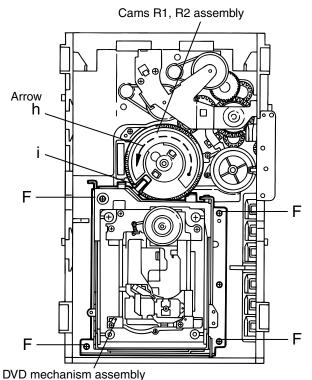

#### Removing the DVD mechanism assembly(See Fig.10)

- 1. While turning the cams R1 and R2 assembly in the arrow direction **h** , align the shaft **i** of the DVD mechanism assembly to the position shown in Fig.10.

- 2. Remove the four screw **F** retaining the DVD mechanism assembly.

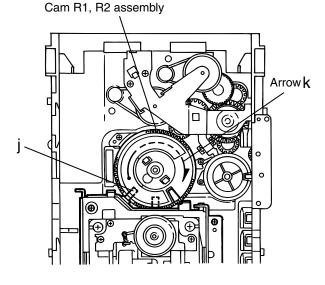

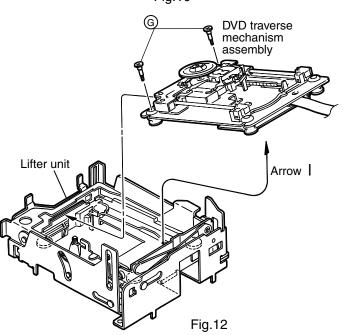

#### Removing the DVD traverse mechanism assembly (See Fig.11 and 12)

- For dismounting only the DVD mechanism without removing the DVD mechanism assembly, align the shaft j of the DVD mechanism assembly to the position shown Fig.11 while turning the cam R1 and R2 assembly in the arrow direction k.

- 2. Remove the two screws **G** raising the DVD mechanism assembly.

- 3. Remove the DVD traverse mechanism assembly in the arrow direction I from the lifter unit (See Fig. 12)

Fig.10

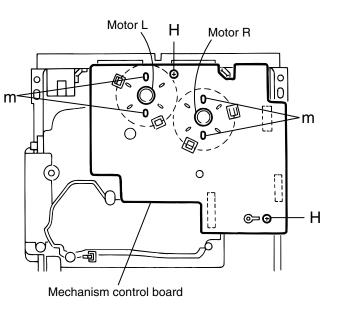

#### Removing the mechanism control board (See Fig.14, 15)

- 1. Absorb the four soldered positions **m** of the right and left motors with a soldering absorber(See Fig.14).

- 2. Remove the two screws **H** retaining the mechanism control board(See Fig.14).

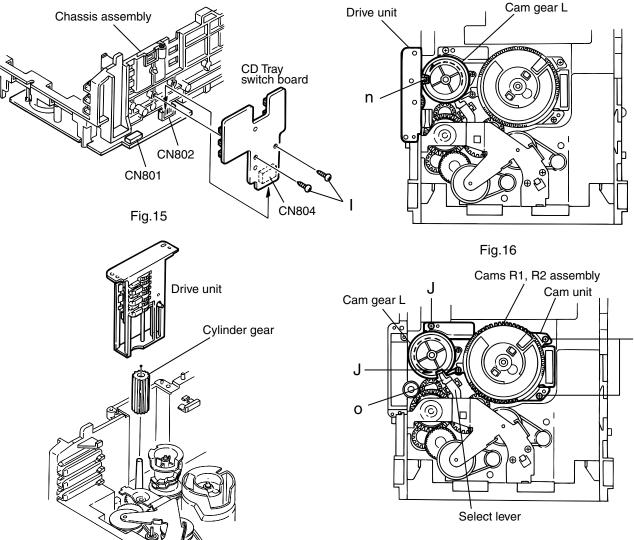

- 3. Remove the two screws **I** retaining the tray select switch board(See Fig.15).

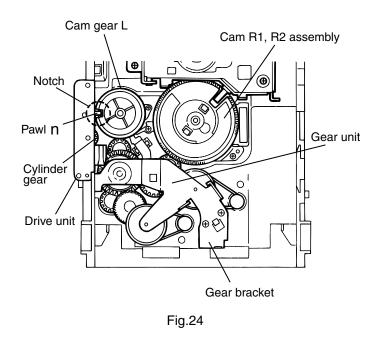

#### ■ Removing the cam unit (See Fig.15 ~ 18)

- 1. Remove the DVD mechanism assembly.

- While turning the cam gear L, align the pawl n position of the drive unit to the notch position(Fig.15) on the cam gear L.

- 3. Pull out the drive unit and cylinder gear(See Fig.17).

- 4. While turning the cam gear L, align the pawl o position of the select lever to the notch position(Fig.18) on the cam gear L.

- 5. Remove the four screws **J** retaining the cam unit(cam gear **L** and cams R1/R2 assembly)(See Fig.18).

Fig.14

Fig.17

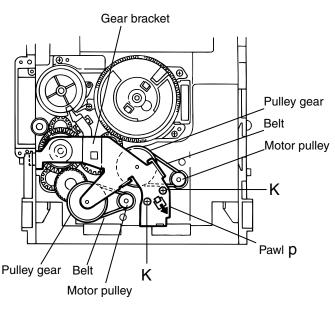

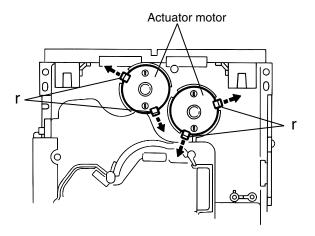

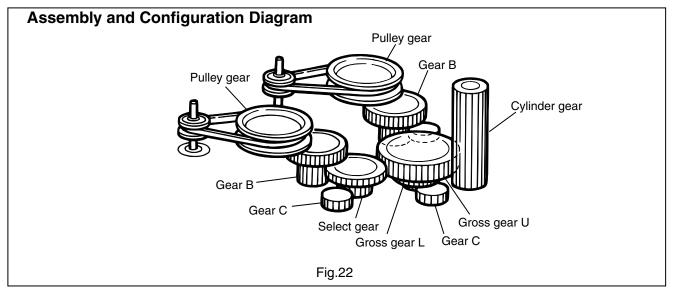

#### ■ Removing the actuator motor and belt (See Fig.19~22)

- 1. Remove the two screws **K** retaining the gear bracket (See Fig.19).

- 2. While pressing the pawl **p** fixing the gear bracket in the arrow direction, remove the gear bracket

(See Fig.19).

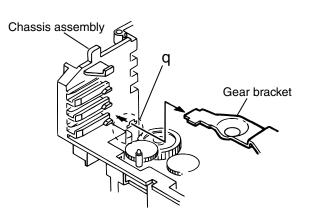

- 3. From the notch **q** section on the chassis assembly fixing the edge of gear bracket, remove and take out the gear bracket(See Fig. 20).

- 4. Remove the belts respectively from the right and left actuator motor pulleys and pulley gears(See Fig. 19).

- 5. After turning over the chassis assembly, remove the actuator motor while spreading the four pawls **r** fixing the right and left actuator motors in the arrow direction(See Fig. 21).

- [Note] When the chassis assembly is turned over under the conditions wherein the gear bracket and belt have been removed, then the pulley gear as well as the gear, etc. constituting the gear unit can possibly be separated to pieces. In such a case, assemble these parts by referring to the assembly and configuration diagram in Fig. 22.

Fig.19

Fig.21

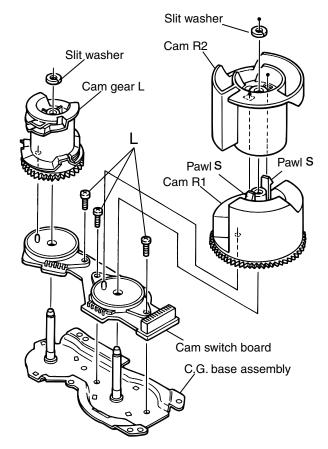

#### Removing the cams R1/R2 assembly and cam gear L (See Fig.23)

- 1. Remove the slit washer fixing the cams R1 and R2 assembly.

- 2. By removing the two pawls **s** fixing the cam R1, separate R2 from R1.

- 3. Remove the slit washer fixing the cam gear  $\ensuremath{\mathsf{L}}.$

- 4. Pull out the cam gear L from the C.G. base assembly.

#### Removing the C.G. base assembly (See Fig.23 and 24)

Remove the three screws  $\,{\rm L\,}\,$  retaining the C.G. base assembly.

[Caution] To reassemble the cylinder gear, etc.with the cam unit (cam gear and cams R1/R2 assembly), gear unit and drive unit, align the position of the pawl n on the drive unit to that of the notch on the cam gear L. Then, make sure that the gear unit is engaged by turning the cam gear L (See Fig. 24).

#### < DVD Traverse mechanism section>

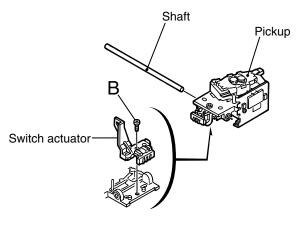

#### Removing the pickup (See Fig.1 to 5)

- 1. Solder soldering **a** on the flexible board next to the pickup unit.

- 2. From the bottom of the traverse mechanism unit, disconnect the flexible wire from CN12 on the pickup board.

#### **ATTENTION**

The laser diode of the pick-up might be destroyed by static electricity, and solder with part a, please before extracting a flexible wire from connector (CN12). Moreover, please remove solder in part a after inserting a flexible wire in connector (CN12). Please refer to page 1-4 for a detailed content.

- 3. Remove the screw **A** attaching the shaft stopper (R) on the upper side of the traverse mechanism unit. Pull the side of the shaft stopper (R) outward to release the joint **b** and remove it upward. Remove the skew spring at the same time.

- 4. Move the shaft in the direction of the arrow to release it from the part **c**.

- 5. Release the joint **d** with the shaft and remove the pickup with the shaft.

- 6. Pull out the shaft.

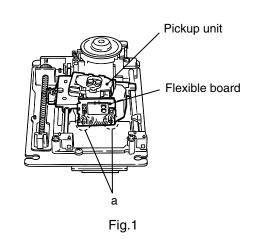

- 7. Remove the screw **B** attaching the switch actuator.

Fig.5

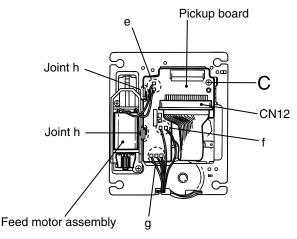

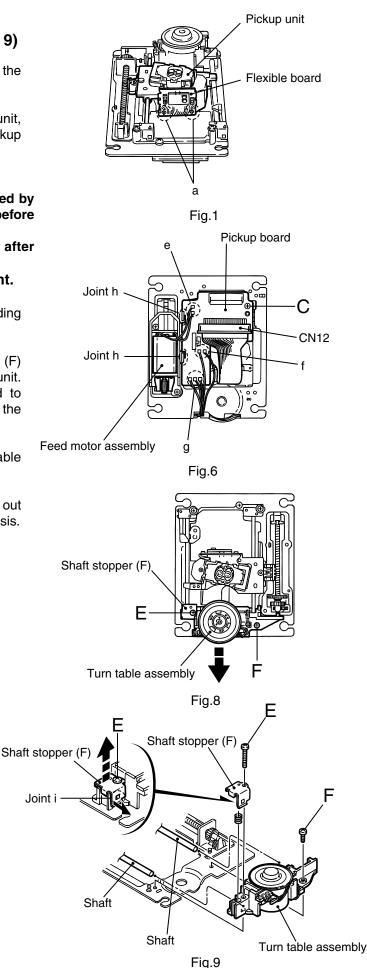

#### ■Removing the pickup board (See Fig 1

(See Fig.1 and 6)

- 1. Solder soldering **a** on the flexible board next to the pickup unit.

- 2. From the bottom of the traverse mechanism unit, disconnect the flexible wire from CN12 on the pickup board.

#### ATTENTION

The laser diode of the pick-up might be destroyed by static electricity, and solder with part a, please before extracting a flexible wire from connector (CN12). Moreover, please remove solder in part a after inserting a flexible wire in connector (CN12). Please refer to page 1-4 for a detailed content.

- 3. Unsolder soldering **e**, **f** and **g** of each harness on the pickup board.

- 4. Remove the screw **C** attaching the pickup board and release the two joints **h**.

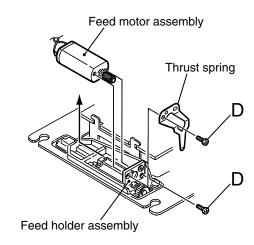

#### Removing the feed motor assembly (See Fig.1, 6 and 7)

- 1. Solder soldering **a** on the flexible board next to the pickup unit.

- 2. From the bottom of the traverse mechanism unit, disconnect the flexible wire from CN12 on the pickup board.

#### ATTENTION

The laser diode of the pick-up might be destroyed by static electricity, and solder with part a, please before extracting a flexible wire from connector (CN12). Moreover, please remove solder in part a after inserting a flexible wire in connector (CN12). Please refer to page 1-4 for a detailed content.

- 3. Unsolder soldering **e** of the motor harness on the pickup board.

- 4. Remove the two screws **D** attaching the feed motor assembly and remove the thrust spring. Move the feed motor assembly in the direction of the arrow to pull it out from the feed holder.

Fig.7

#### Removing the turn table assembly (See Fig.1, 6, 8 and 9)

- 1. Solder soldering **a** on the flexible board next to the pickup unit.

- 2. From the bottom of the traverse mechanism unit, disconnect the flexible wire from CN12 on the pickup board.

#### ATTENTION

The laser diode of the pick-up might be destroyed by static electricity, and solder with part a, please before extracting a flexible wire from connector (CN12). Moreover, please remove solder in part a after inserting a flexible wire in connector (CN12). Please refer to page 1-4 for a detailed content.

- 3. Unsolder soldering **f** and **g** of the harness extending from the turn table assembly to the pickup board.

- 4. Remove the screw E attaching the shaft stopper (F) on the upper side of the traverse mechanism unit. Pull the side of the shaft stopper (F) outward to release the joint i and remove it upward. Remove the spring at the same time.

- 5. Remove the screw **F** attaching the turn table assembly.

- 6. Move the turn table assembly outward and pull out from the shaft. Then remove it from the base chassis.

# Adjustment method

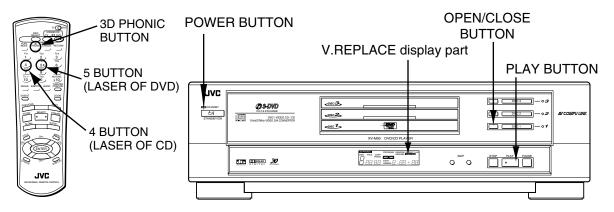

#### (1) Initialization method

If microprocessor (IC401,IC402,IC403) or pick-up is replaces, initialize the DVD player in the following matter

Take out the disc and close the tray.

Unplug the power plug.

Insert power plug into outlet while pressing both PLAY button and DISC 1 OPEN/CLOSE button.

FL Display indicate "tESt \*\* ¥. \*\*Version, ¥Region code

Press 3D-PHONIC key button of remote controller. and EEPROM initialize start.

When indicate "V.REPLACE" on the display, initialize finishes.

The power is turned OFF, and Unplug the power plug.

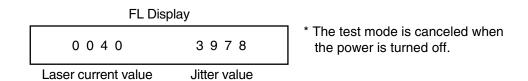

#### (2) Display of "Laser current value" and "Jitter value"

# "Laser current value" and "Jitter value" are displayed on the FL display by the undermentioned method. Please refer to the failure diagnosis.

1)Take out the disc and close the tray.

2)Unplug the power plug.

3) Insert power plug into outlet while pressing both PLAY button and DISC 1 OPEN/CLOSE button.

4)FL Display indicate "tESt \* \* ¥. \* \* Version, ¥Region code

5)Press the "OPEN/CLOSE" button to move the tray outward.

Put the test disc (VT-501) on the tray and press "OPEN/CLOSE" button.

The tray should move inward (Note:Don't push to close the tray directly by hand etc.) 6)Press the "PLAY" button.

7)The laser current value and the jitter value is displayed on the FL indicator as follows.

#### ■ For Laser current value

The laser current value becomes 40mA for the above-mentioned.

Becomes a test mode by doing above-mentioned procedure 1) - 4). Afterwards, the laser current value can be switched by pushing the key to remote control without turning on the disk.

| Remote control | "4" key Laser of CD  |  |

|----------------|----------------------|--|

| Remote control | "5" key Laser of DVD |  |

\*Returns to a usual test mode by the thing to push the stop button of remote control.

If the laser current value is 64mA or less, it is roughly good. There is a possibility to which pick-up is deteriorated, and exchange pick-up, please when there are 65mA or more laser current value.

#### For Jitter value

The jitter value is displayed by the hexadecimal number and refer to the conversion table of following, please. If the indication value is 11% or less, it can be judged by this simple checking method that the signal read precision of the set is satisfactory.

Before using the TEST disc VT-501, careful check it if there is neither damage nor dirt on the read surface.

#### Jitter value

| FL display | Conversion value(&) |

|------------|---------------------|------------|---------------------|------------|---------------------|------------|---------------------|

| 3818       | 4.7                 | 3998       | 7.6                 | 3B18       | 10.5                | 3C98       | 13.3                |

| 3828       | 4.8                 | 39A8       | 7.7                 | 3B28       | 10.6                | 3CA8       | 13.5                |

| 3838       | 4.9                 | 39B8       | 7.8                 | 3B38       | 10.7                | 3CB8       | 13.6                |

| 3848       | 5.1                 | 39C8       | 7.9                 | 3B48       | 10.8                | 3CC8       | 13.7                |

| 3858       | 5.2                 | 39D8       | 8.1                 | 3B58       | 10.9                | 3CD8       | 13.8                |

| 3868       | 5.3                 | 39E8       | 8.2                 | 3B68       | 11.1                | 3CE8       | 13.9                |

| 3878       | 5.4                 | 39F8       | 8.3                 | 3B78       | 11.2                | 3CF8       | 14.1                |

| 3888       | 5.5                 | 3A18       | 8.5                 | 3B88       | 11.3                | 3D18       | 14.3                |

| 3898       | 5.7                 | 3A28       | 8.7                 | 3B98       | 11.4                | 3D28       | 14.4                |

| 38A8       | 5.8                 | 3A38       | 8.8                 | 3BA8       | 11.5                | 3D38       | 14.5                |

| 38b8       | 5.9                 | 3A48       | 8.9                 | 3BB8       | 11.7                | 3D48       | 14.7                |

| 38c8       | 6.0                 | 3A58       | 9.0                 | 3BC8       | 11.8                | 3D58       | 14.8                |

| 38d8       | 6.1                 | 3A68       | 9.1                 | 3BD8       | 11.9                | 3D68       | 14.9                |

| 38E8       | 6.3                 | 3A78       | 9.3                 | 3BE8       | 12.0                | 3D78       | 15.0                |

| 38F8       | 6.4                 | 3A88       | 9.4                 | 3BF8       | 12.1                | 3D88       | 15.1                |

| 3918       | 6.6                 | 3A98       | 9.5                 | 3C18       | 12.4                | 3D98       | 15.3                |

| 3928       | 6.7                 | 3AA8       | 9.6                 | 3C28       | 12.5                | 3DA8       | 15.4                |

| 3938       | 6.9                 | 3AB8       | 9.7                 | 3C38       | 12.7                | 3DB8       | 15.5                |

| 3948       | 7.0                 | 3AC8       | 9.9                 | 3C48       | 12.7                | 3DC8       | 15.6                |

| 3958       | 7.1                 | 3AD8       | 10.0                | 3C58       | 12.9                | 3DD8       | 15.7                |

| 3968       | 7.2                 | 3AE8       | 10.1                | 3C68       | 13.0                | 3DE8       | 15.9                |

| 3978       | 7.3                 | 3AF8       | 10.2                | 3C78       | 13.1                | 3DF8       | 16.0                |

| 3988       | 7.5                 |            |                     | 3C88       | 13.2                |            |                     |

When replacing a pickup etc., execute the following adjustments:

#### **Pickup replacement**

- 1. When removing the traverse mechanism from the changer mechanism unit, move the pickup to the innermost diameter of the disc and set switch (S11) on the pick-up board on "SHORT" side, please before removing the card wire from connector (CN10)

- 2. Take out the traverse mechanism.

- 3. First short-circuit the pickup circuit before removing the pickup. Then carry out the replacement.

# Adjustment

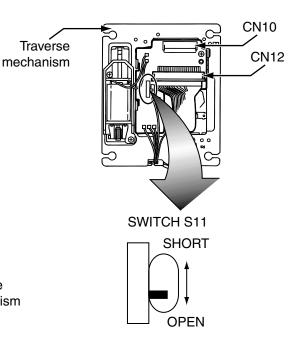

#### Jig setup

- Remove the rubber cushion from each of the four corners of the traverse mechanism. (When installing be sure not to make a mistake with the cushion colors).

- 2. Install the jig stud.

- 3. Make a jig clamp. (Remove the clamp from the set and assemble it as shown in the diagram below.

#### Note:

How to handle the pickup

To protect the pickup from electro-static damage, make sure to hold it by the die-cast chassis (optical base). And make sure that pickup lens do not touch the top cover.

How to prepare a clamp

and holder

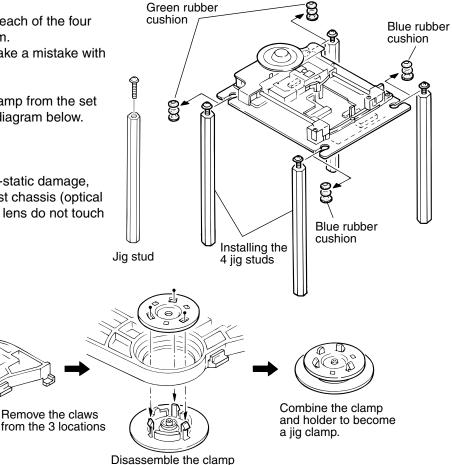

#### Integrated wiring for adjustment

- 1. Place a board on top of the unit and put the changer on it. Then carry out the wiring of the main unit.

- Connect a extension cable to the traverse mechanism for adjustment and then connect them to the changer.

- 3. Remove the solder of the short-circuited flexible wire. Then remove the short-circuited pin from the traverse mechanism

- 4. Connection is completed.

#### Adjustment preparation

- 1. The 3 adjustment locations

- 2. 1.4 mm hexagonal wrench

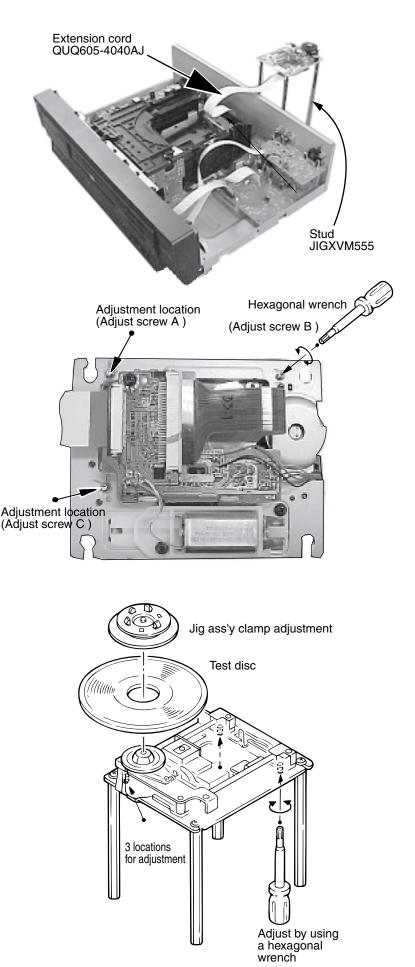

- 3. Set the VT-501 or the VT502 test disc.

#### FL jitter display

- Connect the power cable while pressing the <u>▲</u> (OPEN/CLOSE) button of DISC1 and

- ▷ (PLAY) button simultaneously.

- --- The DISC no. "EESE J /" is displayed on the FL indicator.

- 2. Press the 3D-PHONIC key button of remote controller to commence initialization.

- 3. When the key ▷ (PLAY) is pressed the jitter value is displayed.

- Adjust the jitter value to minimum by using the adjust screw.

- a). Turn the adjustment screw ( A and B ) clockwise half.

- b). Return the adjustment screw ( A and B ) to former position.

- c). Turn the adjustment screw ( A and B ) counterclockwise half.

- d). Set the adjustment screw ( A and B ) to the position of best jitter at three positions.

- Next, do it similar to the above-mentioned in adjustment screw A and C.

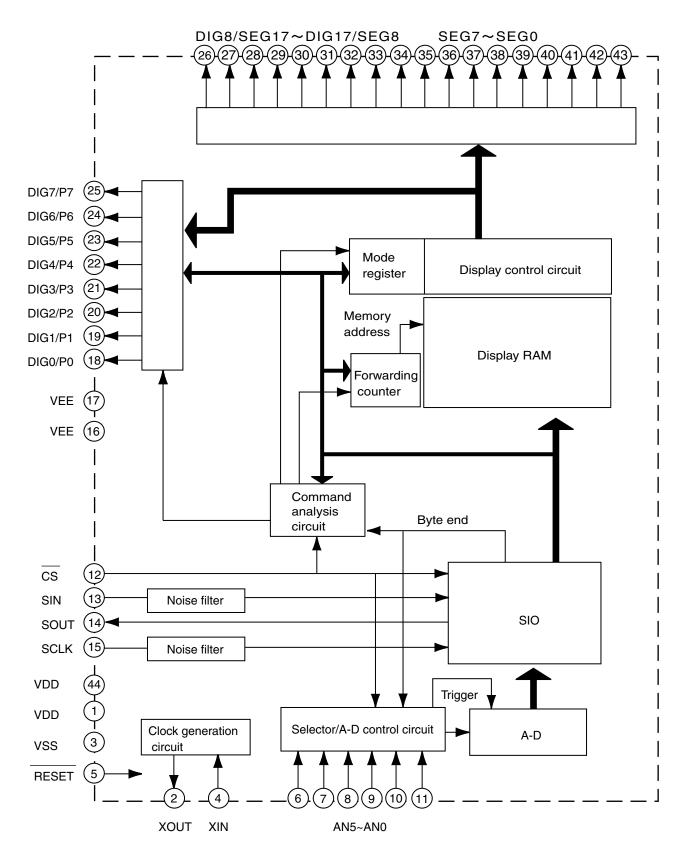

## **Description of major ICs**

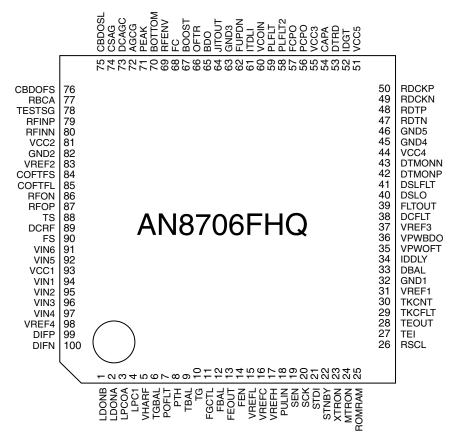

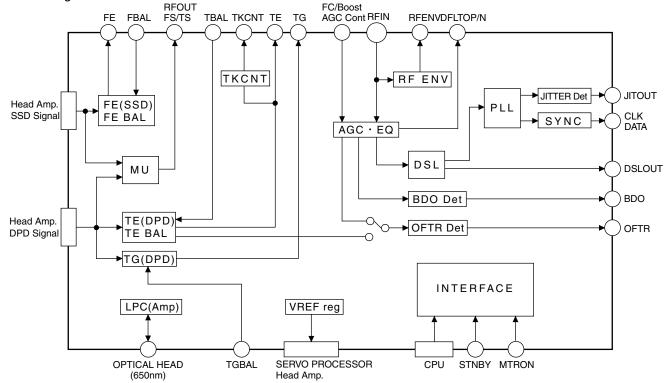

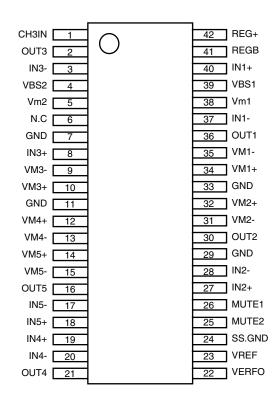

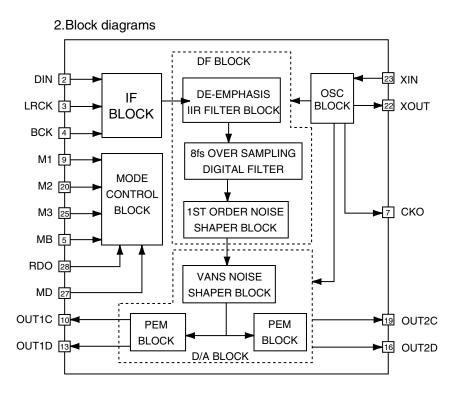

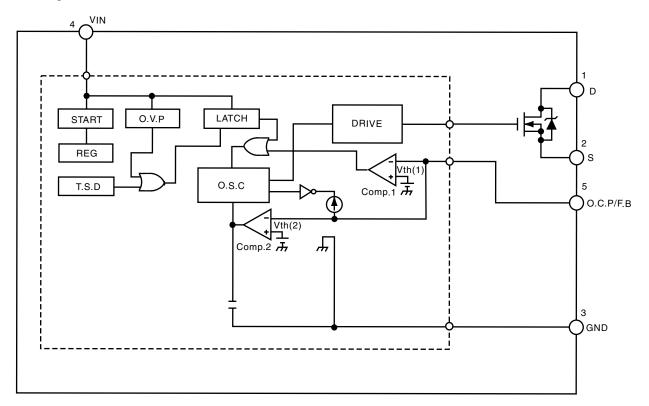

#### AN8706FHQ (IC101) : Front end processor

1.Pin layout

2.Block diagram

#### 3.Pin function

| functior | า      |          | AN8706FHQ (1/2)                                                                |

|----------|--------|----------|--------------------------------------------------------------------------------|

| Pin No.  | Symbol | I/O      | Functions                                                                      |

| 1        | LDONB  | Ι        | Laser ON (CD Head) terminal                                                    |

| 2        | LDONA  | Ι        | Laser ON (DVD Head) terminal                                                   |

| 3        | LPCOA  | 0        | Laser drive output terminal                                                    |

| 4        | LPC1   | Ι        | Laser PIN input terminal                                                       |

| 5        | VHARF  | 0        | VHALF voltage output terminal                                                  |

| 6        | TGBAL  | Ι        | Tangential phase balance control terminal                                      |

| 7        | POFLT  | 0        | Track detection Threshold value level terminal                                 |

| 8        | PTH    | Ι        | Track detection Threshold value level terminal                                 |

| 9        | TBAL   | Ι        | Tracking balance control terminal                                              |

| 10       | TG     | 0        | Tangential phase error signal output terminal                                  |

| 11       | FGCTL  | Ι        | Focus amplifier Gain control terminal                                          |

| 12       | FBAL   | Ι        | Focus balance control terminal                                                 |

| 13       | FEOUT  | 0        | Focus error signal output terminal                                             |

| 14       | FEN    | -        | Focus error output amplifier reversing input terminal                          |

| 15       | VREFL  | 0        | VREFL voltage output terminal                                                  |

| 16       | VREFC  | 0        | VREFC voltage output terminal                                                  |

| 17       | VREFH  | 0        | VREFH voltage output terminal                                                  |

| 18       | PULIN  |          | DSL,PLL drawing mode switch terminal                                           |

| 19       | SEN    | I        | SEN(Cereal data input terminal)                                                |

| 20       | SCK    | I        | SCK(Cereal data input terminal)                                                |

| 21       | STDI   |          | STDI(Cereal data input terminal)                                               |

| 22       | STNBY  |          | Standby mode control terminal                                                  |

| 23       | XTRON  |          | Tracking OFF holding input terminal                                            |

| 23       | MTRON  | <br>     | Monitor output ON/OFF switch terminal                                          |

| 25       | ROMRAM |          | ROM•RAM switch terminal                                                        |

| 26       | RSCL   | 0        | Standard current source terminal                                               |

| 20       | TEI    |          | Tracking error output amplifier reversing input terminal                       |

|          |        |          |                                                                                |

| 28<br>29 | TEOUT  | 0        | Tracking error signal output terminal<br>Track count detection filter terminal |

| 30       | TKCFLT | 0        |                                                                                |

|          |        | _        | Track count output terminal                                                    |

| 31       | VREF1  | 0        | VREF1 voltage output terminal                                                  |

| 32       | GND1   | 0        | Earth terminal 1                                                               |

| 33       | DBAL   | <u> </u> | Data slice offset adjustment terminal                                          |

| 34       | IDDLY  | <u> </u> | Data slice delay adjustment terminal                                           |

| 35       | VPWOFT | <u> </u> | OFTR detection level setting terminal                                          |

| 36       | VPWBDO |          | BDO detection level setting terminal                                           |

| 37       | VREF3  | 0        | VREF3 voltage output terminal                                                  |

| 38       | DCFLT  | 0        | Capacity connection terminal for data slice input filter                       |

| 39       | FLTOUT | 0        | Filter amplifier output terminal                                               |

| 40       | DSLO   | 0        | Data slice single data output terminal                                         |

| 41       | DSLFLT | 0        | Data slice time constant filter terminal                                       |

| 42       | DTMONP | 0        | PLL differential motion 2 making to value edge signal moniter output (+)       |

| 43       | DTMONN | 0        | PLL differential motion 2 making to value edge signal moniter output (-)       |

| 44       | VCC4   |          | Power terminal 4 (5V)                                                          |

| 45       | GND4   | 0        | Earth terminal 4                                                               |

| 46       | GND5   | 0        | Earth terminal 5                                                               |

| 47       | RDTN   | 0        | PLL differential motion making to synchronization RF signal reversing output   |

| 48       | RDTP   | 0        | PLL differential motion making to synchronization RF signal rotation output    |

| 49       | RDCKN  | 0        | PLL differential motion making synchronization clock reversing output          |

| 50       | RDCKP  | 0        | PLL differential motion making synchronization clock rotation output           |

|         |        |     | AN8706FHQ(2/2)                                               |

|---------|--------|-----|--------------------------------------------------------------|

| Pin No. | Symbol | I/O | Functions                                                    |

| 51      | VCC5   | Ι   | Power terminal 5 (3.3V)                                      |

| 52      | IDGT   | Ι   | Data slice address part gate signal input terminal (For RAM) |

| 53      | DTRD   | Ι   | Data slice data read signal input terminal(For RAM)          |

| 54      | CAPA   | Ι   | Data slice CAPA(Address)signal input terminal (For RAM)      |

| 55      | VCC3   | Ι   | Power terminal 3 (5V)                                        |

| 56      | PCPO   | 0   | PLL phase gain set terminal                                  |

| 57      | FCPO   | 0   | PLL frequency gain set terminal                              |

| 58      | PLFLT2 | 0   | PLL low-pass filter terminal                                 |

| 59      | PLFLT  | 0   | PLL high-pass filter terminal                                |

| 60      | VCOIN  | Ι   | PLL VCO input terminal                                       |

| 61      | ITDLI  | 0   | PLL jitter free current ripple removal filter terminal       |

| 62      | FUPDN  | Ι   | PLL frequency control input terminal                         |

| 63      | GND3   | 0   | Earth terminal 3                                             |

| 64      | JITOUT | 0   | Detection signal output of jitter                            |

| 65      | BDO    | 0   | BDO output terminal                                          |

| 66      | OFTR   | 0   | OFTR output terminal                                         |

| 67      | BOOST  | I   | Boost control terminal for filter                            |

| 68      | FC     | I   | FC control terminal for filter                               |

| 69      | RFENV  | 0   | RF envelope output terminal                                  |

| 70      | воттом | 0   | Bottom envelope detection filter terminal                    |

| 71      | PEAK   | 0   | Peak envelope detection filter terminal                      |

| 72      | AGCG   | 0   | AGC amplifier gain control terminal                          |

| 73      | DCAGC  | 0   | AGC amplifier filter terminal                                |

| 74      | CSAG   | 0   | Sag cancellation circuit filter terminal                     |

| 75      | CBDOSL | 0   | BDO detection capacitor terminal                             |

| 76      | CBDOFS | 0   | BDO detection capacitor terminal                             |

| 77      | RBCA   | 0   | BCA detection level setting terminal                         |

| 78      | TESTSG | 1   | TEST signal input terminal                                   |

| 79      | RFINP  | I   | RF signal positive input terminal                            |

| 80      | RFINN  | I   | RF signal negative input terminal                            |

| 81      | VCC2   | I   | Power terminal 2 (5V)                                        |

| 82      | GND2   | 0   | Earth terminal 2                                             |

| 83      | VREF2  | 0   | VREF2 voltage output terminal                                |

| 84      | COFTFS | 0   | OFTR detection capacitor terminal                            |

| 85      | COFTFL | 0   | OFTR detection capacitor terminal                            |

| 86      | RFON   | 0   | RF signal output terminal N                                  |

| 87      | RFOP   | 0   | RF signal output terminal P                                  |

| 88      | TS     | 0   | Full adder amplifier (DVD) output terminal                   |

| 89      | DCRF   | 0   | Full adder amplifier capacitor terminal                      |

| 90      | FS     | 0   | Full adder amplifier (CD) output terminal                    |

| 91      | VIN6   |     | Focus input of external division into two terminal           |

| 92      | VIN5   | I   | Focus input of external division into two terminal           |

| 93      | VCC1   | I   | Power terminal 1 (5V)                                        |

| 94      | VIN1   | I   | External division into four (DVD/CD) RF input terminal 1     |

| 95      | VIN2   | I   | External division into four (DVD/CD) RF input terminal 2     |

| 96      | VIN3   |     | External division into four (DVD/CD) RF input terminal 3     |

| 97      | VIN4   | ·   | External division into four (DVD/CD) RF input terminal 4     |

| 98      | VREF4  | 0   | VREF4 voltage output terminal                                |

| 99      | DIFP   | 0   | RF signal (RAM) output terminal P                            |

| !       |        |     | RF signal (RAM) output terminal N                            |

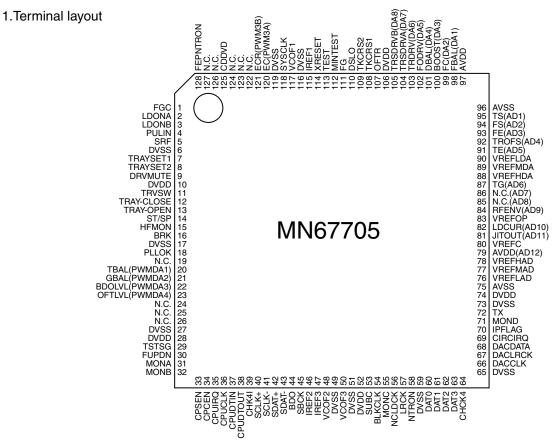

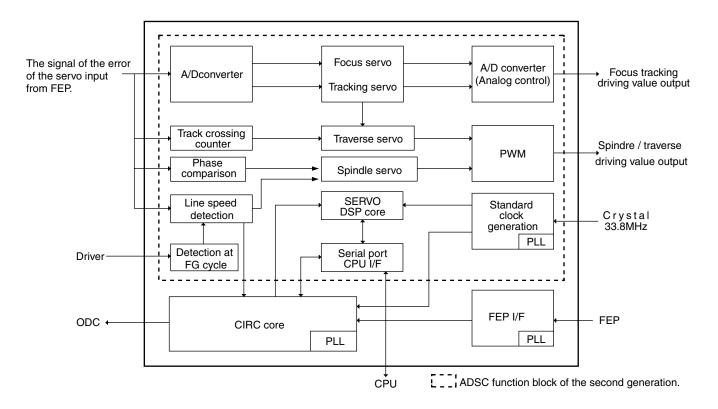

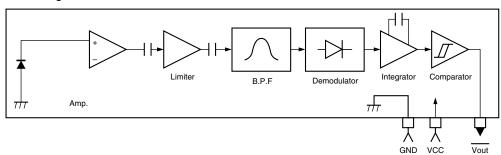

#### MN67705EA (IC201) : Digital servo controller

2.Block diagram

#### 3.Pin function

| Pin No. | Symbol         | I/O | Function                                                 |

|---------|----------------|-----|----------------------------------------------------------|

| 1       | FGC            | 0   | H fixation                                               |

| 2       | LDONA          | 0   | Laser drive controlA (ON / OFF)                          |

| 3       | LDONB          | 0   | Laser drive controlB (ON / OFF)                          |

| 4       | PULIN          | 0   | DSL and PLL high boost signal (FEP)                      |

| 5       | SRF            | 0   | Head amplifier gain H/L selection                        |

| 6       | DVSS           |     | Ground for digital circuit                               |

| 7       | TRAYSET1       | 0   | Tray drive ON/OFF and direction control                  |

| 8       | TRAYSET2       | 0   | Tray drive ON/OFF and direction control                  |

| 9       | DRVMUTE        | 0   | Drive IC mute control                                    |

| 10      | DVDD           |     | Power supply for digital circuit                         |

| 11      | TRVSW          | I   | Surroundings position detection in traverse              |

| 12      | TRAY-CLOSE     | I   | Tray close detection SW                                  |

| 13      | TRAY-OPEN      | I   | Tray opening detection SW                                |

| 14      | ST/SP          | 0   | Spindle motor drive switch (START /STOP)                 |

| 15      | HFMON          | 0   | High cycle module control                                |

| 16      | BRK            | 0   | Spindle motor IC short brake control                     |

| 17      | DVSS           |     | Ground for digital circuit                               |

| 18      | PLLOK          | I   | SYNC detection (DVD : 18T / CD : 22T)                    |

| 19      | N.C.           | 0   |                                                          |

| 20      | TBAL(PWMDA1)   | 0   | Tracking balance (FEP)                                   |

| 21      | GBAL(PWMDA2)   | 0   | Tangential balance (FEP)                                 |

| 22      | BDOLVL(PWMDA3) | 0   | BDO slice level (FEP)                                    |

| 23      | OFTLVL(PWMDA4) | 0   | Off-track error slice level (FEP)                        |

| 24      | N.C.           | 0   |                                                          |

| 25      | N.C.           | 0   |                                                          |

| 26      | N.C.           | 0   |                                                          |

| 27      | DVSS           |     | Ground for digital circuit                               |

| 28      | DVDD           |     | Power supply for digital circuit                         |

| 29      | TSTSG          | 0   | Self calibration signal (FEP)                            |

| 30      | FUPDN          | 0   | Signal of frequency UP/DOWN of PLL (FEP)                 |

| 31      | MONA           | 0   | Monitor terminal A                                       |

| 32      | MONB           | 0   | Monitor terminal B                                       |

| 33      | CPSEN          | I   | Servo DSP serial I/F chip selection (SYSCOM)             |

| 34      | CPCEN          | I   | CIRC serial I/F chip selection (SYSCOM)                  |

| 35      | CPUIRQ         | 0   | Interrupt request to silicon (SYSCOM)                    |

| 36      | CPUCLK         | I   | Silicon serial I/F clock (SYSCOM)                        |

| 37      | CPUDTIN        | I   | Silicon serial I/F data input (SYSCOM)                   |

| 38      | CPUDTOUT       | 0   | Silicon serial I/F data output (SYSCOM)                  |

| 39      | CHK4I          | I   | Connects with unused DVSS                                |

| 40      | SCLK+          | I   | Lead channel clock differential motion signal (positive) |

| 41      | SCLK-          | I   | Lead channel clock differential motion signal (negative) |

| 42      | SDAT+          | I   | Lead channel data differential motion signal (positive)  |

| 43      | SDAT-          | I   | Lead channel data differential motion signal (negative)  |

| 44      | BDO            | I   | BDO + BCA (FEP)                                          |

| 45      | SBCK           | I   | CD sub-code data shift clock (ODC)                       |

| 46      | IREF2          | _   | Connects with unused DVSS                                |

| MN | 6770 | 5FA | (2/3) |

|----|------|-----|-------|

|    | 0110 |     | (2,0) |

|         |              | 1        | MN67705EA (2/3)                                                |

|---------|--------------|----------|----------------------------------------------------------------|

| Pin No. | Symbol       | I/O      | Function                                                       |

| 47      | IREF3        | —        | Connects with unused DVSS                                      |

| 48      | VCOF2        | —        | Connects with unused DVSS                                      |

| 49      | DVSS         | —        | Ground for digital circuit                                     |

| 50      | VCOE3        | —        | Connects with unused DVSS                                      |

| 51      | DVSS         | —        | Ground for digital cirucuit                                    |

| 52      | DVDD         | _        | Power supply for digital cirucuit                              |

| 53      | SUBC         | 0        | CD sub-code (ODC)                                              |

| 54      | BLKCLK       | 0        | CD sub-code synchronous signal (ODC)/Jump output of one at DVD |

| 55      | MONC         | 0        | Monitor terminal C                                             |

| 56      | NCLDCK       | 0        | Sub-code data frame clock (ODC)                                |

| 57      | LRCK         | 0        | LR channnel data strove CIRC(ODC)                              |

| 58      | NTRON        | 0        | L: Tracking ON (ODC)                                           |

| 59      | DVSS         |          | Ground for digital cirucuit                                    |

| 60      | DAT0         | 0        | CIRC / Binary making DVD data output                           |

| 61      | DAT1         | 0        | CIRC / Binary making DVD data output                           |

| 62      | DAT2         | 0        | CIRC / Binary making DVD data output                           |

| 63      | DAT3         | 0        | CIRC / Binary making DVD data output                           |

| 64      | CHCK4        | 0        | Synchronous clock of DAT0~3                                    |

| 65      | DVSS         | _        | Ground for digital circuit                                     |

| 66      | DACCLK       | 0        |                                                                |

| 67      | DACLRCK      | 1        | Connects with unused DVSS                                      |

| 68      | DACDATA      |          | Connects with unused DVSS                                      |

| 69      | CIRCIRQ      | 0        | RAM with built-in CIRC exceeds / Underflow interrupt           |

| 70      | IPFLAG       | 0        | CIRC error flag                                                |

| 71      | MOND         | 0        | Monitor terminal D                                             |

| 72      | ТХ           | 0        | Digital audio interface                                        |

| 73      | DVSS         | _        | Ground for digital cirucuit                                    |

| 74      | DVDD         |          | Power supply for digital cirucuit                              |

| 75      | AVSS         |          | Ground for analog cirucuit                                     |

| 76      | VREFLAD      | _        | AD subordinate position standard voltage $(0.6 \pm 0.1v)$      |

| 77      | VREFMAD      |          | It is a place standard voltage in AD $(1.4 \pm 0.1V)$          |

| 78      | VREFHAD      | _        | High-ranking AD standard voltage ( $2.2 \pm 0.1V$ )            |

| 79      | AVDD         | _        | Power supply for analog circuit                                |

| 80      | VREFC(AD12)  | 1        |                                                                |

| 81      | JITOUT(AD11) | I        | Jitter signal(FEP)                                             |

| 82      | LDCUR(AD10)  | 1        | Laser drive current signal                                     |

| 83      | VREFOP       |          | Operation amplifier standard voltage(VREFC)                    |

| 84      | RFENV(AD9)   | 1        | RFENV(FEP)                                                     |

| 85      | N.C.(AD8)    | I        | Connects with VREFC                                            |

| 86      | N.C.(AD7)    | 1        | Connects with VREFC                                            |

| 87      | TG(AD6)      | 1        | Tangential Phase difference (FEP)                              |

| 88      | VREFHDA      | -<br>-   | High-ranking AD standard voltage ( $2.2\pm0.1V$ )              |

| 89      | VREFMDA      |          | It is a place standard voltage in AD $(1.4 \pm 0.1V)$          |

| 90      | VREFLDA      |          | AD subordinate position standard voltage $(0.6 \pm 0.1v)$      |

| 91      | TE(AD5)      | 1        | Tracking error (FEP)                                           |

| 92      | TROFS(AD4)   | I        | Tracking drive IC input offset                                 |

| 93      | FE(AD3)      | <u> </u> | Focus error (FEP)                                              |

| 55      |              | •        |                                                                |

|         | 1            |     | MN67705EA (2/3)                                                |

|---------|--------------|-----|----------------------------------------------------------------|

| Pin No. | Symbol       | I/O | Function                                                       |

| 47      | IREF3        |     | Connects with unused DVSS                                      |

| 48      | VCOF2        | _   | Connects with unused DVSS                                      |

| 49      | DVSS         | —   | Ground for digital circuit                                     |

| 50      | VCOE3        |     | Connects with unused DVSS                                      |

| 51      | DVSS         | _   | Ground for digital cirucuit                                    |

| 52      | DVDD         | _   | Power supply for digital cirucuit                              |

| 53      | SUBC         | 0   | CD sub-code (ODC)                                              |

| 54      | BLKCLK       | 0   | CD sub-code synchronous signal (ODC)/Jump output of one at DVD |

| 55      | MONC         | 0   | Monitor terminal C                                             |

| 56      | NCLDCK       | 0   | Sub-code data frame clock (ODC)                                |

| 57      | LRCK         | 0   | LR channnel data strove CIRC(ODC)                              |

| 58      | NTRON        | 0   | L: Tracking ON (ODC)                                           |

| 59      | DVSS         |     | Ground for digital cirucuit                                    |

| 60      | DAT0         | 0   | CIRC / Binary making DVD data output                           |

| 61      | DAT1         | 0   | CIRC / Binary making DVD data output                           |

| 62      | DAT2         | 0   | CIRC / Binary making DVD data output                           |

| 63      | DAT3         | 0   | CIRC / Binary making DVD data output                           |

| 64      | CHCK4        | 0   | Synchronous clock of DAT0~3                                    |

| 65      | DVSS         | _   | Ground for digital circuit                                     |

| 66      | DACCLK       | 0   | 5                                                              |

| 67      | DACLRCK      |     | Connects with unused DVSS                                      |

| 68      | DACDATA      | 1   | Connects with unused DVSS                                      |

| 69      | CIRCIRQ      | 0   | RAM with built-in CIRC exceeds / Underflow interrupt           |

| 70      | IPFLAG       | 0   | CIRC error flag                                                |

| 71      | MOND         | 0   | Monitor terminal D                                             |

| 72      | ТХ           | 0   | Digital audio interface                                        |

| 73      | DVSS         | _   | Ground for digital cirucuit                                    |

| 74      | DVDD         | _   | Power supply for digital cirucuit                              |

| 75      | AVSS         |     | Ground for analog cirucuit                                     |

| 76      | VREFLAD      |     | AD subordinate position standard voltage $(0.6 \pm 0.1 v)$     |

| 77      | VREFMAD      |     | It is a place standard voltage in AD $(1.4\pm0.1V)$            |

| 78      | VREFHAD      |     | High-ranking AD standard voltage $(2.2 \pm 0.1V)$              |

| 79      | AVDD         | _   | Power supply for analog circuit                                |

| 80      | VREFC(AD12)  | I   |                                                                |

| 81      | JITOUT(AD11) | I   | Jitter signal(FEP)                                             |

| 82      | LDCUR(AD10)  |     | Laser drive current signal                                     |

| 83      | VREFOP       | _   | Operation amplifier standard voltage(VREFC)                    |

| 84      | RFENV(AD9)   | I   | RFENV(FEP)                                                     |

| 85      | N.C.(AD8)    | I   | Connects with VREFC                                            |

| 86      | N.C.(AD7)    | I   | Connects with VREFC                                            |

| 87      | TG(AD6)      |     | Tangential Phase difference (FEP)                              |

| 88      | VREFHDA      | _   | High-ranking AD standard voltage ( $2.2 \pm 0.1V$ )            |

| 89      | VREFMDA      |     | It is a place standard voltage in AD $(1.4\pm0.1V)$            |

| 90      | VREFLDA      |     | AD subordinate position standard voltage $(0.6 \pm 0.1v)$      |

| 91      | TE(AD5)      | I   | Tracking error (FEP)                                           |

| 92      | TROFS(AD4)   | I   | Tracking drive IC input offset                                 |

| 93      | FE(AD3)      | I   | Focus error (FEP)                                              |

|         | · · · /      | L   |                                                                |

#### XV-M52SL/XV-M50BK

MN67705EA(3/3)

| Pin No. | Symbol       | I/O | Function                                   |

|---------|--------------|-----|--------------------------------------------|

| 94      | FS(AD2)      | I   | FS (FEP)                                   |

| 95      | TS(AD1)      | I   | TS (FEP)                                   |

| 96      | AVSS         |     | Ground for analog cirucuit                 |

| 97      | AVDD         | _   | Power supply for analog circuit            |

| 98      | FBAL(DA1)    | 0   | Focus balance(FEP)                         |

| 99      | FC(DA2)      | 0   | Cutting off frequency (FEP)                |

| 100     | BOOST(DA3)   | 0   | Amount of boost (FEP)                      |

| 101     | DBAL(DA4)    | 0   | DSL offset balance (FEP)                   |

| 102     | FODRV(DA5)   | 0   | Focus drive                                |

| 103     | TRDRV(DA6)   | 0   | Tracking drive                             |

| 104     | TRSDRVA(DA7) | 0   | Traverse drive A aspect                    |

| 105     | TRSDRVB(DA8) | 0   | Traverse drive B aspect                    |

| 106     | DVDD         |     | Power supply for digital cirucuit          |

| 107     | OFTR         | I   | Off-track error signal (FEP)               |

| 108     | TKCRS1       | I   | Track crossing signal 1 (FEP)              |

| 109     | TKCRS2       | I   | Track crossing signal 2 (FEP)              |

| 110     | DSLO         | I   | Binary making data slice signal (FEP)      |

| 111     | FG           | I   | FG signal input (spindle motor driver)     |

| 112     | MINTEST      |     | Connects with DVSS                         |

| 113     | TEST         | _   | Connects with DVSS                         |

| 114     | XRESET       | I   | Reset L: Reset                             |

| 115     | IREF1        | _   | VCO reference current 1( for SYSCLK)       |

| 116     | DVSS         |     | Ground for digital circuit)                |

| 117     | VCOF1        | _   | VCO control voltage 1 (for SYSCLK)         |

| 118     | SYSCLK       | Ι   | 33.8MHz system clock input                 |

| 119     | DVSS         | —   | Ground for digital circuit                 |

| 120     | EC(PWM3A)    | 0   | Spindle motor drive                        |

| 121     | ECR(PWM3B)   | 0   |                                            |

| 122     | N.C.(PWM3A)  | 0   |                                            |

| 123     | N.C.(PWM2B)  | 0   |                                            |

| 124     | N.C.(PWM1A)  | 0   |                                            |

| 125     | CDDVD        | 0   | CD/DVD control signal (FEP) CD : H DVD : L |

| 126     | N.C.(PWM0A)  | 0   |                                            |

| 127     | N.C.(PWM0B)  | 0   |                                            |

| 128     | FEPNTRON     | 0   | Tracking ON (FEP)                          |

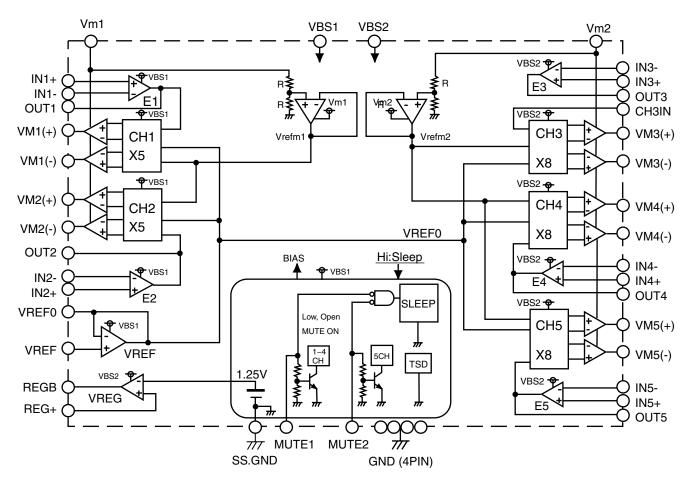

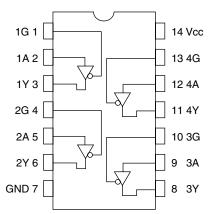

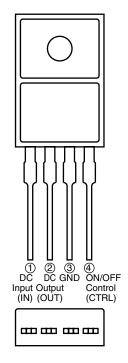

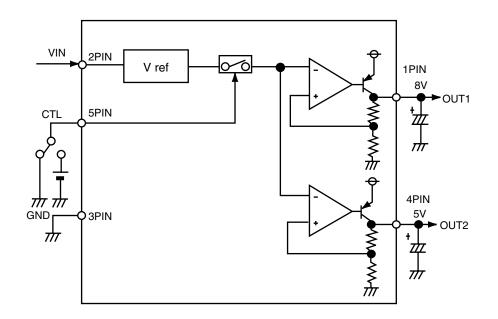

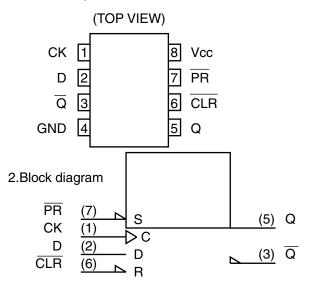

#### M56788FP-W (IC271) : Traverse mechanism driver

#### 1.Terminal layout

#### 2.Block diagram

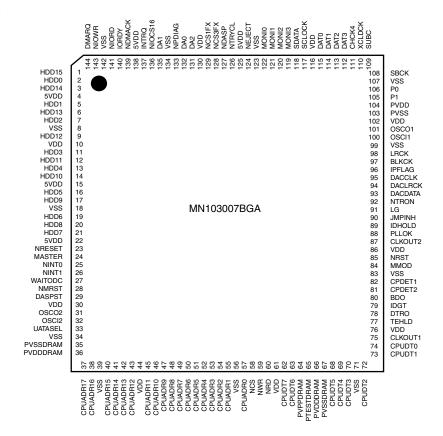

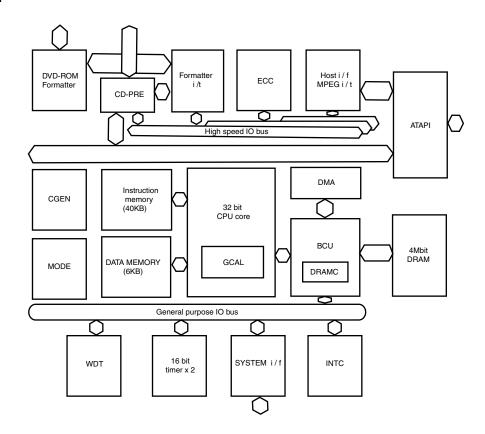

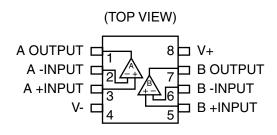

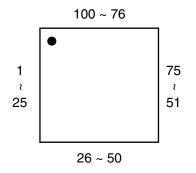

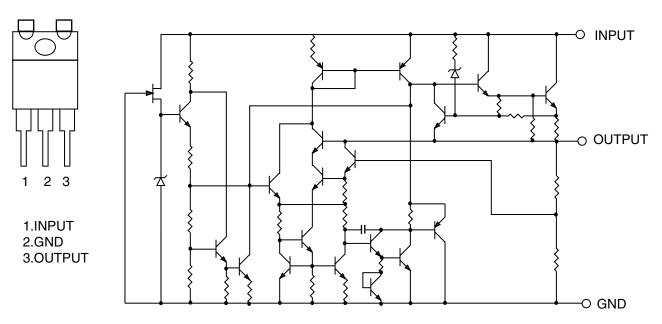

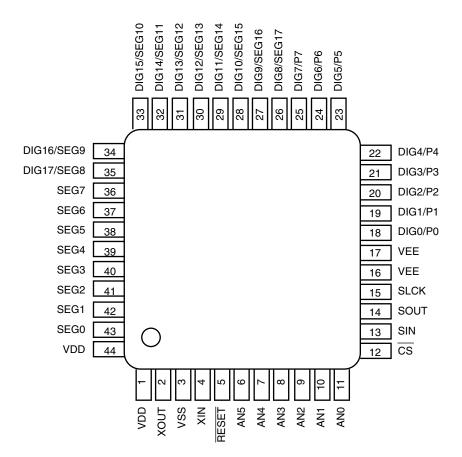

#### MN103007BGA (IC301) : Optical disc controller

1.Terminal layout

2.Block diagram

#### 3.Pin function

|         |          |     | MN103007BGA(1/4)               |

|---------|----------|-----|--------------------------------|

| Pin NO. | Symbol   | 1/0 | Function                       |

| 1       | HDD15    | I/O | ATAPI data                     |

| 2       | HDD0     | I/O | ATAPI data                     |

| 3       | HDD14    | I/O | ATAPI data                     |

| 4       | 5VDD     |     |                                |

| 5       | HDD1     | I/O | ATAPI data                     |

| 6       | HDD13    | I/O | ATAPI data                     |

| 7       | HDD2     | I/O | ATAPI data                     |

| 8       | VSS      |     |                                |

| 9       | HDD12    | I/O | ATAPI data                     |

| 10      | VDD      |     |                                |

| 11      | HDD3     | I/O | ATAPI data                     |

| 12      | HDD11    | I/O | ATAPI data                     |

| 13      | HDD4     | I/O | ATAPI data                     |

| 14      | HDD10    | I/O | ATAPI data                     |

| 15      | 5VDD     |     |                                |

| 16      | HDD5     | I/O | ATAPI data                     |

| 17      | HDD9     | I/O | ATAPI data                     |

| 18      | VSS      |     |                                |

| 19      | HDD6     | I/O | ATAPI data                     |

| 20      | HDD8     | I/O | ATAPI data                     |

| 21      | HDD7     | I/O | ATAPI data                     |

| 22      | 5VDD     |     |                                |

| 23      | NRESET   | I   | ATAPI reset                    |

| 24      | MASTER   | I/O | ATAPI master / slave selection |

| 25      | NINT0    | 0   | System control interruption 0  |

| 26      | NINT1    | 0   | System control interruption 1  |

| 27      | WAITODC  | 0   | System control weight control  |

| 28      | NMRST    | 0   | System control reset           |

| 29      | DASPST   |     | DASP signal initializing       |

| 30      | VDD      |     |                                |

| 31      | OSCO2    | I,O | VSS connection, OPEN           |

| 32      | OSCI2    | I,O | VSS connection, OPEN           |

| 33      | UATASEL  |     | VSS connection                 |

| 34      | VSS      |     |                                |

| 35      | PVSSDRAM |     |                                |

| 36      | PVDDDRAM |     |                                |

| 37      | CPUADR17 |     | System control address         |

| 38      | CPUADR16 |     | System control address         |

| 39      | VSS      |     |                                |

| 40      | CPUADR15 |     | System control address         |

| 41      | CPUADR14 | 1   | System control address         |

| 42      | CPUADR13 | 1   | System control address         |

| 43      | CPUADR12 |     | System control address         |

| 44      | VDD      |     | System control address         |

| 45      | CPUADR11 |     | System control address         |

| MN103007BGA(2/4) |

|------------------|

|          |           |     | MN103007BGA(2/4)                          |

|----------|-----------|-----|-------------------------------------------|

| Pin NO.  | Symbol    | I/O | Function                                  |

| 46       | CPUADR10  |     | System control address                    |

| 47       | CPUADR9   |     | System control address                    |

| 48       | CPUADR8   |     | System control address                    |

| 49       | CPUADR7   | I   | System control address                    |

| 50       | CPUADR6   | I   | System control address                    |

| 51       | CPUADR5   | 1   | System control address                    |

| 52       | CPUADR4   |     | System control address                    |

| 53       | CPUADR3   |     | System control address                    |

| 54       | CPUADR2   |     | System control address                    |

| 55       | CPUADR1   | 1   | System control address                    |

| 56       | VSS       |     | GND                                       |

| 57       | CPUADR0   | -   | System control address                    |

| 58       | NCS       |     | System control chip select                |

| 59       | NWR       |     | System control write                      |

| 60       | NRD       |     | System control read                       |

| 61       | VDD       |     | Apply 3V                                  |

| 62       | CPUDT7    |     | System control data                       |

| 63       | CPUDT6    |     | System control data                       |

| 64       | PVPPDRAM  | 0   | C=10000PF is connected between VSS        |

| 65       | PTESTDRAM |     | VSS connected                             |

| 66       | PVDDDRAM  |     |                                           |

| 67       | PVSSDRAM  |     |                                           |

| 68       | CPUDT5    |     | System control data                       |

| 69       | CPUDT4    |     | System control data                       |

| 70       | CPUDT3    |     | System control data                       |

| 71       | VSS       |     | GND                                       |

| 72       | CPUDT2    |     | System control data                       |

| 73       | CPUDT1    | I/O | System control data                       |

| 74       | CPUDT0    | I/O | System control data                       |

| 75       | CLKOUT1   | 0   | 16.9/11.2/8.45MHz clock                   |

| 76       | VDD       |     | Apply 3V                                  |

| 77       | TEHLD     | 0   | Mirror gate                               |

| 78       | DTRO      | 0   | Data part frequency control switch        |

| 79       | IDGT      | 0   | Part CAPA switch                          |

| 80       | BDO       |     | RF dropout / BCA data of making to binary |

| 81       | CPDET2    | 1   | Outer side CAPA detection                 |

| 82       | CPDET1    |     | Side of surroundings on inside            |

| 83       | VSS       | I   | GND                                       |

| 84       | MMOD      |     | VSS connected                             |

| 85       | NRST      |     | System reset                              |

| 86       | VDD       | I   | Apply 3V                                  |

| 87       | CLKOUT2   | -   | 16.9MHz clock                             |

| 88       | PLLOK     | 0   | Frame mark detection                      |

| 89       | IDHOLD    | 0   | ID gate for tracking holding              |

| 89<br>90 | JMPINH    | 0   | Jump prohibition                          |

| 90       |           | 0   |                                           |

MN103007BGA(3/4)

|         |         |      | MN103007BGA(3/4)                              |  |

|---------|---------|------|-----------------------------------------------|--|

| Pin NO. | Symbol  | I/O  | Function                                      |  |

| 91      | LG      | 0    | Land / group switch                           |  |

| 92      | NTRON   | Ι    | Tracking ON                                   |  |

| 93      | DACDATA | 0    | Serial output                                 |  |

| 94      | DACLRCK | 0    | L and R identification output                 |  |

| 95      | DACCLK  | Ι    | Clock for serial output                       |  |

| 96      | IPFLAG  | 1    | Interpolation flag input                      |  |

| 97      | BLKCK   | Ι    | Sub-code,Block clock input                    |  |

| 98      | LRCK    | Ι    | L and R identification signal output          |  |

| 99      | VSS     |      | · ·                                           |  |

| 100     | OSCI1   | I,O  | 16.9MHz oscillation                           |  |

| 101     | OSCO1   | I,O  | 16.9MHz oscillation                           |  |

| 102     | VDD     |      |                                               |  |

| 103     | PVSS    |      |                                               |  |

| 104     | PVDD    |      |                                               |  |

| 105     | P1      | I/O  | Terminal MASTER polarity switch input         |  |

| 106     | P0      | I/O  | CIRC-RAM OVER/UNDER                           |  |

|         |         |      | Interruption signal input                     |  |

| 107     | VSS     |      |                                               |  |

| 108     | SBCK    | 0    | Sub-code, Clock output for serial input       |  |

| 109     | SUBC    | 1    | Sub-code, Serial input                        |  |

| 110     | XCLDCK  | 1    | Sub-code, Frame clock input                   |  |

| 111     | CHCK4   |      | Read clock to DAT3~0                          |  |

|         |         |      | (Output of dividing frequency four from ADSC) |  |

| 112     | DAT3    | 1    | Read data from DISC                           |  |

| 113     | DAT2    | I    | (Parallel output from ADSC)                   |  |

| 114     | DAT1    | I    | (                                             |  |

| 115     | DAT0    |      |                                               |  |

| 116     | VDD     |      |                                               |  |

| 117     | SCLOCK  | I/O  | Debugging serial clock                        |  |

|         |         |      | (270Ω pull up)                                |  |

| 118     | SDATA   | I/O  | Debugging serial data                         |  |

|         |         |      | $(270 \Omega \text{ pull up})$                |  |

| 119     | MONI3   | 0    | Internal goods title monitor                  |  |

| 120     | MONI2   | 0    |                                               |  |

| 121     | MONI1   | 0    |                                               |  |

| 122     | MONI0   | 0    |                                               |  |

| 123     | VSS     |      |                                               |  |

| 124     | NEJECT  | Ι    | Eject detection                               |  |

| 125     | 5VDD    |      |                                               |  |

| 126     | NTRYCL  | I    | Tray close detection                          |  |

| 127     | NDASP   | I/O  | ATAPI Drive active/                           |  |

|         |         |      | Slave connection I/O                          |  |

| 128     | NCS3FX  | Ι    | ATAPI host chip select                        |  |

| 129     | NCS1FX  | Ι    | ATAPI host chip select                        |  |

| 130     | VDD     |      |                                               |  |

| 131     | DA2     | I/O  | ATAPI host address                            |  |

| 132     | DA0     | I/O  | ATAPI host address                            |  |

|         |         | ., 🦉 |                                               |  |

# XV-M52SL/XV-M50BK

| MN103007BGA(4/4) |  |

|------------------|--|

|------------------|--|

| Pin NO. | Symbol  | I/O | Function                                            |

|---------|---------|-----|-----------------------------------------------------|

| 133     | NPDIAG  | I/O | ATAPI slave master diagnosis input                  |

| 134     | VSS     |     |                                                     |

| 135     | DA1     | I/O | ATAPI host address                                  |

| 136     | NIOCS16 | 0   | ATAPI output of selection of width of host data bus |

| 137     | INTRQ   | 0   | ATAPI host interruption output                      |

| 138     | 5VDD    |     |                                                     |

| 139     | NDMACK  | I   | ATAPI host DMA response                             |

| 140     | IORDY   | 0   | ATAPI host ready output                             |